PCIe无疑是最为流行的传输总线标准,这几年的更新换代也十分频繁:PCIe 3.0目前还是最普及的,PCIe 4.0随着2019年AMD锐龙3代和EPYC2处理器也在逐步推广中,PCIe 5.0也预计在2021年和英特尔下一代至强sapphire rapids上获得支持。其实PCie的下一代标准也在快速推进中。

PCI-SIG组织近日宣布,PCIe 6.0规范已经完成了0.5版本,并提供给组织成员,将在明年按期发布最终正式版。根据以往的静音,在0.5版本发布之后,已经算形成基本框架了,厂商们可以开始设计测试芯片,为后续的推进工作提前做好准备。

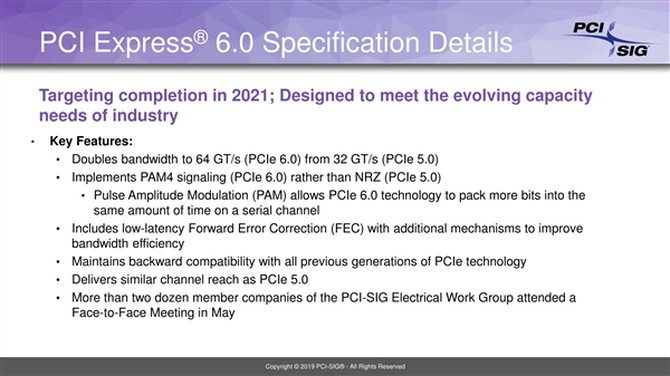

PCIe 6.0将延续PCIe 3.0时代引入的128b/130b编码方式,但加入全新的脉冲幅度调制PAM4,取代PCIe 5.0 NRZ,可以在单个通道、同样时间内封包更多数据,以及低延迟前向纠错(FEC)和相关机制,以改进带宽效率。

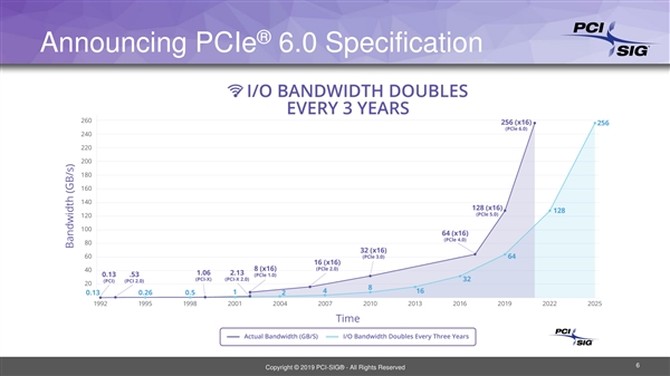

在向下兼容PCIe 5.0/4.0/3.0/2.0/1.0的同时,PCIe 6.0数据率或者说I/O带宽会再次加倍来到64GT/s,PCIe 6.0 x1单向实际带宽8GB/s,PCIe 6.0 x16单向带宽128GB/s、双向带宽256GB/s。

今年的PCI-SIG开发者大会将于6月初举行,届时会有超过25家组织成员对PCIe 6.0规范进行进一步探讨,我们将获得更多的具体信息。