我们知道,在2008年末AMD发布了45nm工艺的CPU,但它并不是采用High-K栅介质的技术,而Intel的High-K技术肯定是未来半导体工艺发展方向,相信全球有制造能力的半导体生产线都将在32nm时使用该类技术,且必须使用该类技术。我们看到,虽然现有非Intel技术的45nm甚至不久后的40nm已经诞生,但在成品的功耗控制方面却大大落后于Intel的45nm技术,而今天我们在Intel 32nm技术上将再次验证HighK带来的低功耗的神奇。

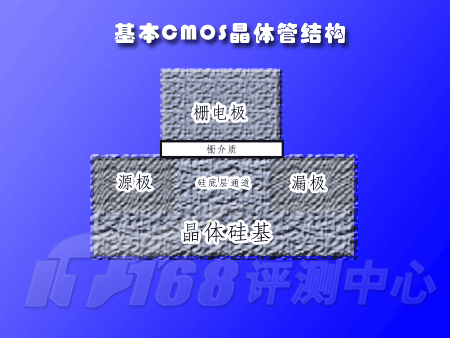

32纳米制程技术的基础是第二代高k+金属栅极晶体管。英特尔对第一代高k+金属栅极晶体管进行了众多改进。 在45纳米制程中,高k电介质的等效氧化层厚度为1.0纳米。而在32纳米制程中,此氧化层的厚度仅为0.9纳米,而栅极长度则缩短为30纳米。

晶体管的栅极间距每两年缩小0.7倍——32纳米制程采用了业内最紧凑的栅极间距。32纳米制程采用了与英特尔45纳米制程一样的置换金属栅极工艺流程,这样有利于英特尔充分利用现有的成功工艺。这些改进对于缩小集成电路(IC)尺寸、提高晶体管的性能至关重要。采用高k+金属栅极晶体管的32纳米制程技术可以帮助设计人员同时优化电路的尺寸和性能。

由于氧化层厚度减小,栅极长度缩短,晶体管的性能提高了22%以上。这些晶体管的驱动电流和栅极长度创造了业内非常好的纪录。此外,漏电电流也得到了优化。与45纳米制程相比,NMOS晶体管的漏电量减少5倍多,PMOS晶体管的漏电量则减少10倍以上。由于上述改进,电路的尺寸和性能均可得到显著优化。除此之外,32纳米还采用了第四代应变硅技术,用于提高晶体管的性能——这样一来,英特尔便可争取更多的时间和机会进行更多技术创新。